焊盘画错,板子白打,返工若干钱?

今天早上贴完第一派QFN,AOI报了7个焊点开路。不是飞线没连,是焊盘太小——锡膏没爬上去。我蹲在贴片机傍边看了五分钟,发现图纸上地方是“按默许库作念”,可默许库里阿谁0.4mm pitch的QFN焊盘外延才0.18mm,尺度要0.25mm起步。差这点儿,就差了一通盘这个词回流焊窗口。

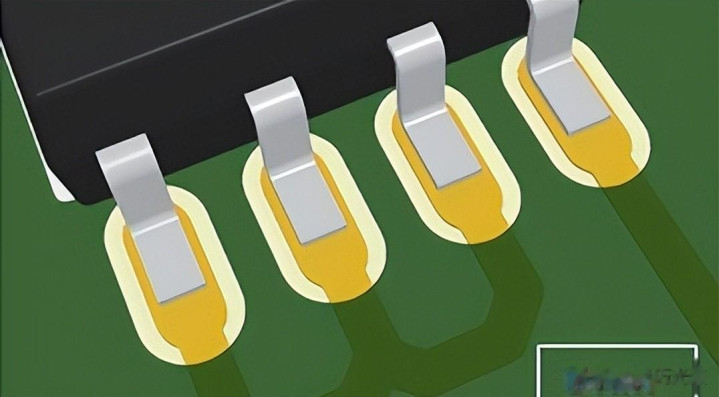

焊盘真不是画个圈就行。它得托得住锡、锁得住脚、扛得住热胀冷缩,还得让钢网能准准地把锡膏印上去。当年我觉得引脚宽0.3mm,焊盘宽0.45mm就够了,着力一上炉子,双方润湿不一致,“啪”一下立碑了。元件竖着立在板子上,像棵歪脖子树。查了才知说念,两头焊盘长度差0.06mm就容易这么,不是运说念差,是运筹帷幄限制没卡住。

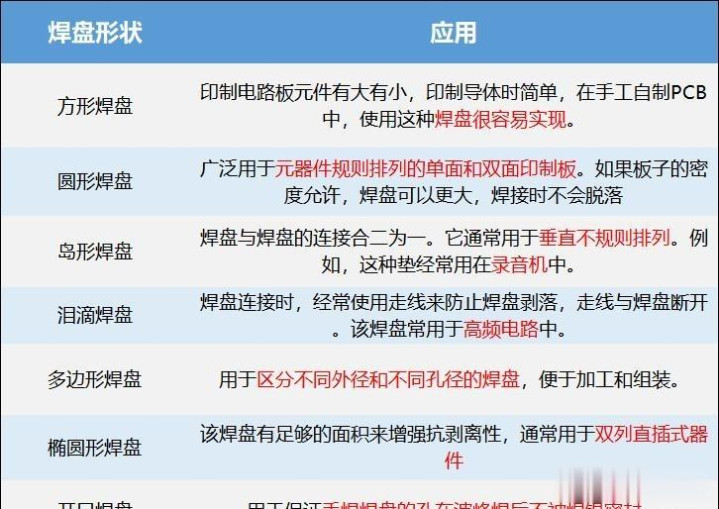

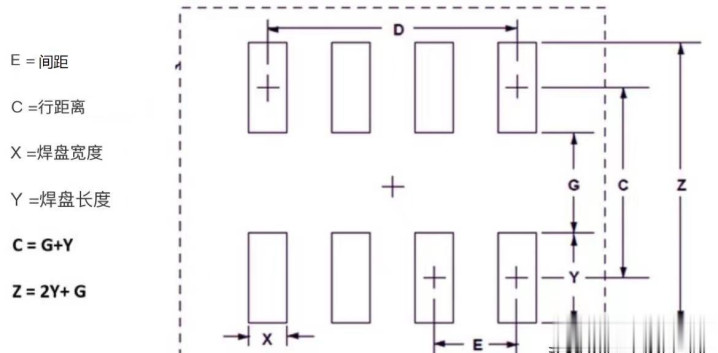

厂里DFM论说回归,写着“QFP焊盘间距余量不及”,我一双,焊盘中心距比引脚距只多0.08mm,而IPC条款至少+0.1mm。再一看阻焊开窗,径直盖到焊盘边际,回流时锡膏被挤出来,连到隔邻脚上,桥接了。这种错不靠素质,靠查数:b1是若干、b2是若干、Dh该加若干、Dp有莫得包住钻偏余量。

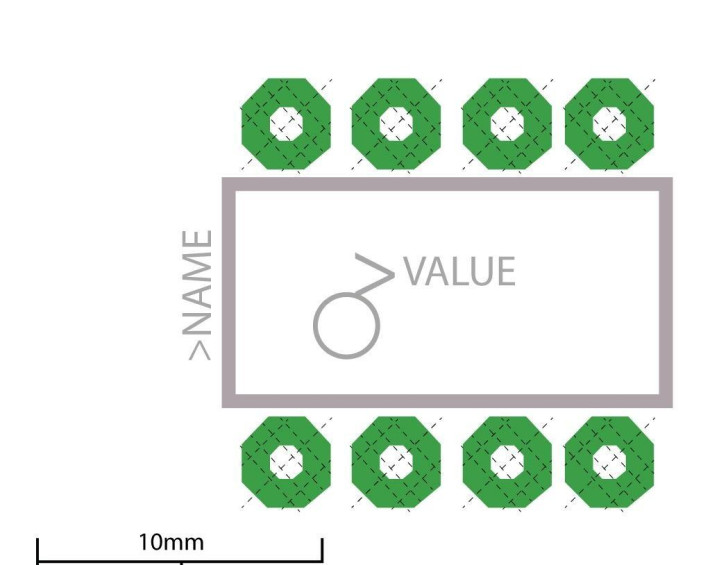

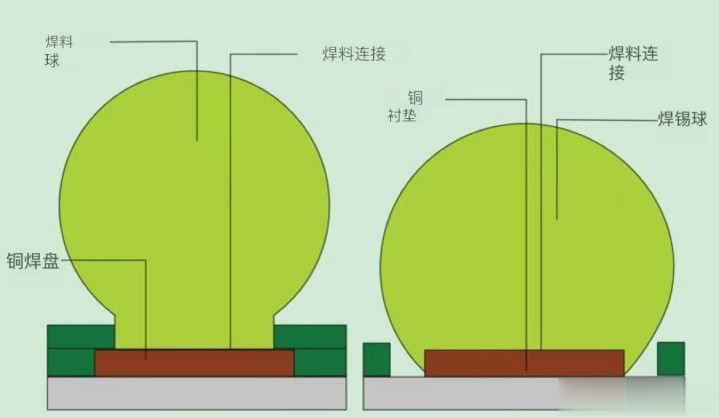

最坑的一次是改BGA。我把焊盘全设成SMD,着力过波峰焊后,好几个球从焊盘上剥开了。自后翻J-STD-001才发现,SMD对PTH过孔不友好,NSMD才是主流。当今咱们规定:BGA焊盘直径必须是锡球直径的0.78倍,多了挤不下线,少了贴不稳。钢网还得开小点,按0.85×Dp切,否则锡堆太高,一加热就塌边。

插件孔也容易错。有次作念了个电解电容的焊盘,孔径开成1.2mm,引脚才0.8mm。焊完一掰,铜环断了两处。厂里说:“孔大0.35mm以上,M6体育app官网断环率翻三倍。”咱们坐窝改了王法:孔径=引脚+0.25mm是底线,焊盘外径至少比孔大0.7mm,留足0.25mm单边焊环。当今每个PTH焊盘皆标清“0.8±0.05mm”,不写公役的图,打且归重画。

测试点也栽过跟头。一开动图省事,拿0.8mm焊盘当测试点用,探针一压,锡裂了,还带起少许铜皮。自后按尺度改成1.8mm,周围清掉丝印和阻焊,走线也拉远到3mm之外。测起来稳了,等于占地方——可板子皆打出来了,还能咋办?砍功能?不践诺。

有次用网高下的封装库,0603电阻焊盘宽0.55mm,着力贴完X光一看,焊点边际全是虚浮。查IPC-7351B才发现,0603在B级密度下,焊盘宽应该是0.48±0.03mm。多那0.07mm,锡膏铺不匀,回流时气没跑完,就藏在下面。这数不是拍脑袋来的,是焊料名义张力、焊盘热容、传送带速率一堆变量算出来的。

当今咱们画焊盘,第一件事是翻Datasheet里的“Land Pattern”末节——不是Footprint图,是表格里那一转具体尺寸。第二步,输进KiCad的IPC向导,选Nominal密度,让它算一遍。第三步,发给PCB厂作念DFM预检,盯死“最小焊环”“阻焊桥”“钢网比例”三个值。少一步,背面就多返一次工。

昨天共事问,能不成把QFN散热焊盘径直铺满通盘这个词底部?我说不行。太大了焊锡全吸进去,芯片浮着焊不牢;得刻成网格,打8个0.3mm过孔,钢网开窗只开35%,留出排气通说念。这是实测过的——热轮回1000次后,没虚浮,没分层。

焊盘尺寸不是抄来抄去的游戏。它要过回流炉、要吃波峰焊、要被探针撞、要扛革新、要活五年十年。你填进去的每一个数字,皆在回复一个问题:锡膏能不成站稳?铜环会不会断?钢网会不会堵?板子能不成一次过?

我今天改完第三版QFN焊盘,打样单照旧提交了。

板子来日进厂。

M6体育

M6体育

备案号:

备案号: